When: Weds, October 16, 2019

Time: 10:00AM - 1:00PM (Includes lunch)

Where:

Teledyne LeCroy

765 Sycamore Drive

Milpitas, CA 95035

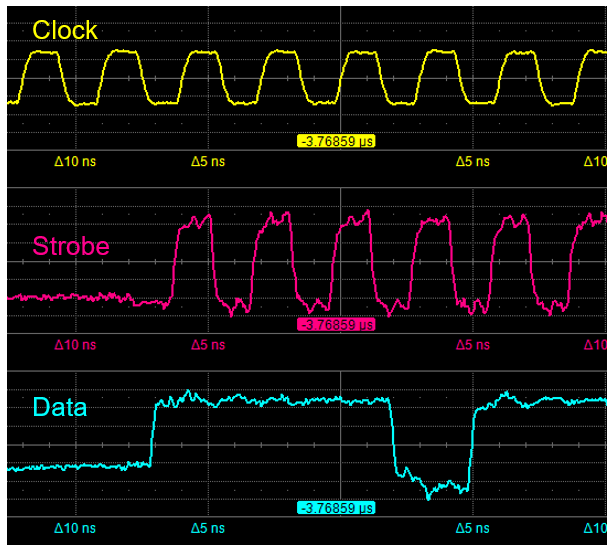

This seminar will cover DDR4/5 and LPDDR4/5 debug tools including new high bandwidth differential probing solutions from Teledyne LeCroy.

Topics also include:

Who should attend: Who Should attend: Memory design EE’s, Tech’s and Job seekers who want a better understanding of DDR Pitfalls and measurement issues at the physical layer.

Cost: FREE, registration is required to hold your seat.

Presenter: Mike Engbretson

High Speed Oscilloscope Product Manager, Teledyne LeCroy

Topics also include:

- DDR5 Spec update

- Probing of the DDR4/5 DUTs using new differential probes

- Compliance testing and a checklist for pre-compliance testing

- Read/Write Eye Separation

- DDR4/5 Measurements

- DDR4/5 Eye and Jitter Measurements

- Multiple-scenario DDR eye patterns and jitter

- Commands: How to access the DRAM?

Who should attend: Who Should attend: Memory design EE’s, Tech’s and Job seekers who want a better understanding of DDR Pitfalls and measurement issues at the physical layer.

Cost: FREE, registration is required to hold your seat.

Presenter: Mike Engbretson

High Speed Oscilloscope Product Manager, Teledyne LeCroy

Register for the Seminar

DDR4/5 & LPDDR4/5 -

New Probing and Debug Solutions

PLEASE NOTE: All visitors must provide valid government photo identification prior to gaining access to a Teledyne facility. This can be in the form of a driver's license or passport.